# ゲートドライブ電源を利用した MOSFET スイッチングアシスト回路の設計法

学生員 村田 宗洋\* 正 員 野口 季彦(静岡大学)

Design Approach of MOSFET Switching Assist Circuit Using Gate Drive Power Supply Munchiro Murata\*, Toshihiko Noguchi (Shizuoka University)

This paper describes a circuit parameter design of a MOSFET switching assist auxiliary circuit fed by a gate drive power supply. The circuit parameters are derived mathematically by two approaches. By applying the designed circuit parameters to a chopper and a half-bridge inverter, a turn-off time of the MOSFET can be effectively reduced, which allows a high-frequency drive and reduction of the switching loss. It has been confirmed through experimental tests that the turn-off dv/dt of the MOSFET can be increased 9 times of the conventional circuit by employing the proposed method, especially in a low-load range.

**キーワード**: MOSFET, 高速スイッチング, パラメータ設計, ターンオフ, 補助回路, チョッパ, インバータ (MOSFET, high-speed switching, parametric design, turn-off, auxiliary circuit, chopper, inverter)

## 1. はじめに

今後、SiC (Silicon Carbide) -MOSFET に代表される新しい電力用半導体スイッチング素子が実用化され、パワーエレクトロニクス分野へ広く普及すると予想されている。従来の Si (Silicon) を基材とする電力用半導体スイッチング素子と比べて、SiC-MOSFET は高耐圧、高温動作、高速スイッチング、低損失など数々の特長をもっており、電力変換器のパワー密度を飛躍的に向上させる切札と期待されている。しかし、一般に MOSFET では低オン抵抗や大電流化に伴って各種寄生容量が増加する傾向にあり、SiC素子ではその固有物性も相伴って、さらに寄生容量が増大すると考えられる。これにより、入力容量や出力容量の高速充放電が妨げられ、本来有している高速スイッチング特性を十分に発揮することが困難となる。

高速スイッチングを実現するためには、ターンオン時間だけでなくターンオフ時間を短縮することが求められる。ターンオン時間は入力容量を高速に充電することにより短縮することができる。従来採用されている手法としては、ゲート抵抗を小さくすることやゲート抵抗と並列にスピードアップコンデンサを用いることが挙げられる。近年では新しいゲート駆動回路の研究も行われており、筆者らはインダクタインパルス重畳方式を用いた超高速スイッチングゲート駆動回路を提案した(1)。一方、ターンオフ時間は出力容量を充電する時間によって決定される。筆者らは主回路の負荷素子と並列にスイッチングアシスト補助回路を設け

ることでターンオフ時間を短縮する手法やゲート駆動回路 にゲートドライブ電源昇圧補助回路を設けてターンオフ時間を短縮する手法を提案している<sup>(2)~(5)</sup>。しかし、ゲートドライブ電源昇圧補助回路のパラメータ設計に関しては詳しい報告を行っていない。

そこで、本稿ではゲートドライブ電源昇圧補助回路の動作原理を述べるとともに、補助回路のパラメータ設計を 2 通りの手法を用いて検討する。ここで述べる MOSFET のスイッチングアシストとは、ソフトスイッチングを目的とするものではなく、ハードスイッチングの dv/dt を高めて高速かつ高効率なスイッチングを可能にするものである。設計したパラメータを用いたゲートドライブ電源昇圧補助回路を降圧チョッパとハーフブリッジインバータに適用し、実験を通じて運転特性を検証した。提案する手法で MOSFETを高速スイッチングすることにより、降圧チョッパでは軽負荷領域においてオンデューティサイクルを 14.4 pt 改善し、ハーフブリッジインバータでも軽負荷領域において 9.0 pt の効率改善を実験的に確認したので報告する。

### 2. ゲートドライブ電源昇圧補助回路

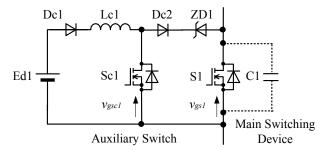

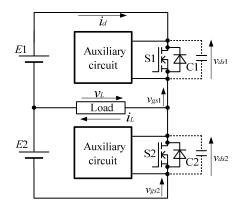

**〈2·1〉 補助回路の構成** 図 1 にゲートドライブ電源 昇圧補助回路を示す。C1 は主スイッチング素子である MOSFET の出力容量を示しており、スナバ回路ではない。 補助回路はゲートドライブ電源 Ed1、補助ダイオード Dc1、 Dc2、インダクタ Lc1、ツェナーダイオード ZD1、補助素子 Sc1 から構成される。S1 と Sc1 のソースが Ed1 と共通であ

図1 ゲートドライブ電源昇圧補助回路

Fig. 1. Voltage boost auxiliary circuit fed by gate drive power supply.

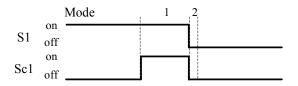

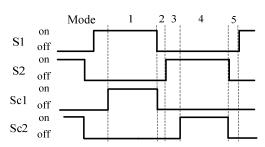

図2 補助回路のスイッチングパターン

Fig. 2. Switching pattern of auxiliary circuit.

るため、S1 と Sc1 を単一のドライブ電源で駆動することが可能である。

Sc1 は高周波駆動が可能でスイッチング損失が少ない寄生容量の小さな素子を選ぶことが望ましい。また、Sc1 の耐圧は S1 と同程度の素子、電流容量は S1 より小さい素子を使用することができる。ZD1 は S1 がオンしているときに補助回路から主回路に電流が流入するのを防ぐため、Dc1、Dc2 は主回路から補助回路に電流が流れるのを防ぐために必要である。1 個あたりの電流耐量が小さいため、ZD1 には 3素子を並列に接続する。

〈2·2〉 補助回路の動作原理 降圧チョッパやハーフ ブリッジインバータなどの電力変換器の従来回路では主素 子がターンオフすると出力容量の充電が開始される。この とき, 出力容量の充電時間は負荷抵抗と出力容量の時定数 によって決定される。このため、重負荷のときはターンオ フ時間が短く,軽負荷のときはターンオフ時間が長くなる。 そこで、提案回路では S1 をオフする直前までインダクタ Lc1 にエネルギーを蓄えておき、S1 をオフした直後に Sc1 をオフすることで C1 を高速充電することにより, 軽負荷領 域においても高速なスイッチングを実現する。図 2 に補助 回路のスイッチングパターンを示す。Mode1 で S1 がオン している期間中に Sc1 をオンすることによって Ed1→Dc1→Lc1→Sc1→Ed1 の経路で電流が流れ Lc1 にエネ ルギーを蓄える。Mode2 で S1 がオフした直後に Sc1 をオフ することによってEd1→Dc1→Lc1→Dc2→ZD1→C1→Ed1の 経路でインパルス状の電流を流して高速に C1 を充電する。 このとき, 充電にかかる時間は Lc1 と C1 の共振周波数の 1/4 周期で決定される。

〈2·3〉 補助回路の設計 提案する補助回路を用いて 高速スイッチングを行うとき、Lc1 に蓄えたエネルギーを C1 に転送するため(1)を満たす必要がある。

$$\frac{1}{2}C1E^2 = \frac{1}{2}Lc1I^2 \tag{1}$$

ここで、E は S1 がオフしているときに S1 にかかる電圧、I は Lc1 に流れる電流のピーク値である。I は Ed1、Lc1、Sc1 のオン時間 t によって決定され(2)となる。

$$I = \frac{Ed1}{Lc1}t\tag{2}$$

(2)を(1)に代入することによって Lc1 に蓄えられるエネルギーと C1 に蓄えられるエネルギーの釣り合い条件は(3)のように表わされる。

$$C1E^2 = \frac{Ed1^2}{Lc1}t^2\tag{3}$$

C1, E, Ed1 のパラメータは与えられているため、Lc1 と t を決定すればよい。そこで、Lc1 と t について拘束条件を定め、2 種類の式を用いることによって補助回路のパラメータを決定する。

まず、Lc1 を決めてから t を導出する手法を述べる。C1 の充電時間はLc1 と C1 の共振周期の 1/4 で決定されるため、動作周期 T の x %を充電に充てるとすれば Lc1 は(4)となる。

$$Lc1 = \frac{4x^2T^2}{\pi^2C1} \tag{4}$$

これより、補助素子のオン時間 t は(3), (4)より(5)のように求めることができる。

$$t = \frac{E}{Ed1} \frac{2xT}{\pi} \tag{5}$$

t は動作周期 T によって制限を受けるため、t が一定の時間 に達したらこの条件は使わないものとする。このような場合は、決定したx を  $x_u$  (制限値)、導出した t を  $t_c$  (計算値) とする。

次に、t を決めてから Lc1 を導出する手法を検討する。補助素子のオン時間をt とすると Lc1 は(3)より(6)となる。

$$Lc1 = \left(\frac{Ed1}{E}\right)^2 \frac{t^2}{C1} \tag{6}$$

また, (6)よりxは(7)と求めることができる。

$$x = \frac{\pi}{2T} \frac{Ed1}{E} t \tag{7}$$

x が過度に大きいと高速スイッチングを目的とした補助回路の効果が半減してしまうため、x が一定の割合に達したらこの条件は使わないものとする。このとき、決定した t を  $t_u$  (制限値)、導出した x を  $x_c$  (計算値)とする。

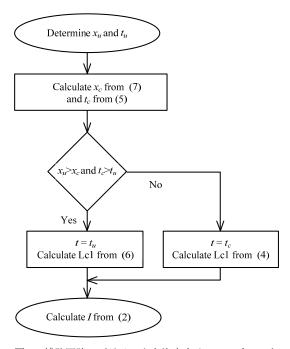

図 3 補助回路のパラメータを決定するフローチャート Fig. 3. Flow chart to determine parameter of auxiliary circuit.

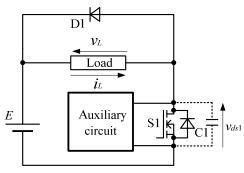

図4 補助回路つき降圧チョッパ

Fig. 4. Proposed buck chopper with auxiliary circuit.

以上のように 2 つの拘束条件を設けることによって 2 種類の式を導出し、それぞれの計算値が制限値を越えないという条件下で補助回路のパラメータを決定する。図 3 に補助回路のパラメータを決定するフローチャートを示す。始めに設定値である  $x_u$ ,  $t_u$  を決定する。次に(5)と(7)より計算値 $x_c$ ,  $t_c$ を求める。計算値が設定値より大きくなった場合には、その条件は使えなくなるため $x_u>x_c$ かつ  $t_c>t_u$ の場合は $t=t_u$ として、Lc1 を(6)より導出する。一方、 $x_c>x_u$ かつ  $t_u$  > $t_c$  の場合は $t=t_c$ として、Lc1 を(4)より導出する。 $x_u=x_c$  かつ  $t_c=t_u$  の場合はどちらの条件を使用してもよい。最後に(2)で求めた Lc1 と t を代入することによって補助素子の電流定格を決定する。以上より補助回路のパラメータ設計に必要な Lc1, t, t を決定する。なお、前述のとおり ZD1 は Ed1 と同じ電圧の素子を用いる。

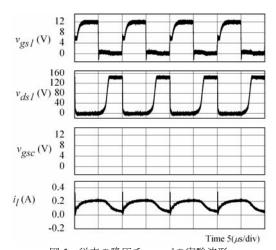

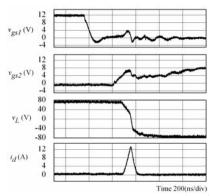

図 5 従来の降圧チョッパの実験波形 Fig. 5. Experimental waveforms of conventional buck chopper.

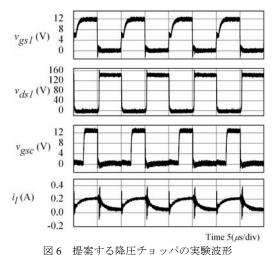

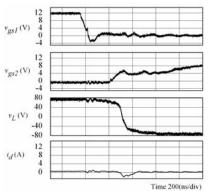

図 6 提条する降圧プヨッハの美験波形 Fig. 6. Experimental waveforms of proposed buck chopper.

#### 3. 実検による動作特性の検証

$\langle 3\cdot 1 \rangle$  降圧チョッパ 図 4 に SI のドレインーソースに補助回路を設けた主回路構成を示す。従来回路では SI がオフしてから CI が充電される時間,すなわちターンオフ時間は SI の出力容量と負荷抵抗の時定数で決定されていた。したがって,負荷電流が小さい軽負荷時にはターンオフ時間が長くなる。そこで,提案回路では SI をオフした直後に ScI をオフすることで Lc1 に蓄えたエネルギーを C1 に転送することで高速充電を行い,負荷電流によらない高速なスイッチングを実現する。

提案した手法の有効性を確認するため、補助回路を降圧チョッパに適用して実機検証を行った。スイッチングパターンは図 2 に示したとおりである。主回路の電源電圧 E を 140 V, E Coss = 2000 pF)、動作周波数 100 kHz という条件において補助回路のパラメータを設計した。 $x_u = 2.5$  %、 $t_u = 4$   $\mu$ s と決定したとき,(5) と(7) より  $x_c = 5.3$  %、 $t_c = 1.8$   $\mu$ s となる。よって $t_c > t_c$  かつ  $t_u > t_c$  であるため  $t = t_c$  となり  $t_c = 1.3$   $t_c = 1.3$   $t_c = 1.4$  と導出される。しかし,導出は全て理想状態で計算したが実際には補助ダイオードの Vf などで損失があるため,ここ

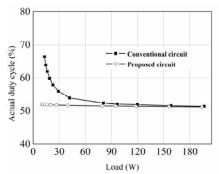

図 7 負荷一実際のオンデューティサイクル特性 Fig. 7. Load-actual on-duty cycle characteristic.

Fig. 8. Load-efficiency characteristic.

では t=3  $\mu$ s として(1)を満たすように調節した。また,(2) より I=2.8 A となるため,Sc1 には ST 製 P12NM60(550 V,12 A),Dc1 および Dc2 には infineon 製 D06S60(600 V,6 A),ZD1 には ON Semiconductor 製 1N5349BG(12 V,5 W)を 3 並列で用いた。

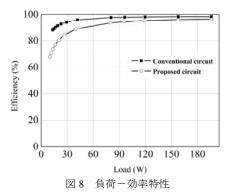

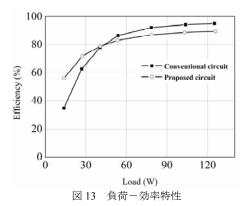

従来回路および提案回路で駆動周波数 100 kHz, デューテ ィサイクル 50 %, 負荷素子のパラメータを 800  $\Omega$  -0.8 mH とした場合の動作波形を図5、図6に示す。図5から読み取 れるように、従来回路ではS1のドレイン-ソース電圧vds1 の立ち上がりが遅いことが確認できる。これは、負荷抵抗 の値が大きいために C1 の充電に時間がかかり, ターンオフ 時間が長くなって高速スイッチングできていないことを表 している。一方、図6からわかるように、提案回路では vds1 が急速に立ち上がっている。デューティーサイクル 50 %駆 動時における実際の vds1 のオンデューティサイクルは従来 回路と提案回路でそれぞれ 66.4%, 52.0%となった。また、 ターンオフ dv/dt はそれぞれ 0.16  $kV/\mu s$ , 1.49  $kV/\mu s$  であり, 提案回路では約 9 倍の高速スイッチングを実現できること がわかる。負荷力率 0.85 を一定としたときの負荷電力と実 際のオンデューティサイクルを図 7 に示し、負荷電力と効 率の関係を図8に示す。図7より従来回路に比べて提案回 路の方が、高周波動作時でもデューティサイクル 50%に近 い運転を維持できることが確認できる。軽負荷領域では負 荷電流が小さいので, 従来回路では C1 を充電する時間が負 荷抵抗と出力容量の時定数で決定されターンオフに長時間 を要するのに対して, 提案回路では負荷に無関係にほぼ一 定の時間で充電が可能である。一方、重負荷時においては

図 9 補助回路つきハーフブリッジインバータ Fig. 9. Proposed half-bridge inverter with auxiliary circuit.

図 10 補助回路付きインバータのスイッチングパターン

Fig. 10. Switching pattern of inverter with auxiliary circuit.

従来回路と提案回路はどちらもほぼデューティーサイクル 50%に近い運転を行うことができる。これは、重負荷の場合は負荷電流が大きく、従来回路においても C1 を高速に充電できるためである。ただし、提案回路においても常に 1.5 pt 程デューティサイクル 50%からの乖離が見られるが、これは C1 で決定される C1 の充電時間によるものである。x=2%であり設計値との間に 0.5 pt の誤差が認められるが、これは C1 の値がドレインーソース間にかかる電圧によって変化するためであると考えられる。また、図 8 に示したように従来回路に比べ提案回路は低効率であり、 13 W 出力時において効率は 15 pt 悪化した。これは、提案回路では補助回路によるスイッチング損および導通損が発生し、これらの損失が付加されたためである。

〈3・2〉ハーフブリッジインバータ 図9にハーフブリッジインバータの上アームと下アームの主素子 S1 と S2 に補助回路を設けた提案回路を示す。前述のとおり C1 と C2 は主スイッチング素子の出力容量を表している。

従来回路では主素子のターンオフ時間は出力容量と負荷抵抗の時定数で決定される。そのため軽負荷時においてはデッドタイム期間中に出力容量の電荷を消費できず高速スイッチングが困難となる。また、S1 がターンオンするときに C1 の電荷を回収しないまま S1 をターンオンすると、単純に C1 に蓄えられたエネルギーが消費されるとともに  $E1 \rightarrow S1 \rightarrow C2 \rightarrow E2 \rightarrow E1$  の経路で大きな短絡電流が流れる。このときの短絡電流は数十 A となり、主素子の損失原因にもなる。そこで、提案回路では S1 をオフした直後に Sc1 をオ

図 11 従来インバータの S1 ターンオフ実験波形 Fig. 11. Experimental waveforms of S1 turn-off in conventional inverter

図 12 提案インバータの S1 ターンオフ実験波形 Fig. 12. Experimental waveforms of S1 turn-off in proposed inverter.

フすることにより高速かつ高効率なスイッチングを実現する。

提案した手法の有効性を確認するために補助回路をハー フブリッジインバータに適用して実機検証を行った。図 10 にスイッチングパターンを示す。E1 および E2 を 70 V, Ed1, および Ed2 を 12 V、S1 および S2 には ST 製 Y60NM60(600 V, 60A, Coss = 2000 pF), 動作周波数 100 kHz, デッドタイ ム 250 ns という条件において補助回路のパラメータを設計 した。デッドタイムが終わる前に出力容量の充電を終える ため  $x_u = 1.5$  %,  $t_u = 4 \mu s$  と決定したとき, (5)と(7)より  $x_c =$ 5.3 %,  $t_c$  = 1.1  $\mu$ s と導かれる。よって, $x_c > x_u$  かつ  $t_u > t_c$  であ るため  $t=t_c$  となり(4)より Lc1 = 4.5  $\mu$ H と導出される。しか し、降圧チョッパの場合と同様に導出は全て理想状態で計 算を行い、またハーフブリッジインバータの場合は出力容 量を充電する際に C1 に流れる電流と E1 に流れる電流に分 流するため $t=2\mu s$ として(1)を満たすように調節した。また, (2)より *I* = 5.3 A となるため、Sc1 には ST 製 P12NM60 (550 V, 12 A), Dc1 には infineon 製 IDH12S60C (600 V, 12 A), Dc2 には infineon 製 D06S60 (600 V, 6 A), ZD1 には ON Semiconductor 製 1N5349BG (12 V, 5 W) を 3 並列で用いた。 下アームの補助回路パラメータは上アームと同一の物を用 いた。

従来回路および提案回路でデューティーサイクルを 50 %, デッドタイムを 250 ns, 負荷素子を 200  $\Omega$ -0.2 mH とした場合の動作波形を図 11, 図 12 に示す。図 11 より従

Fig. 13. Load-efficiency characteristic.

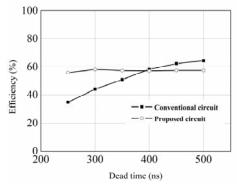

図14 デッドタイム-効率特性

Fig. 14. Dead time-efficiency characteristic.

来回路ではデッドタイム期間終了後 S2 がオンするときに, C1 の電荷を放電できていないため、電源が短絡され大きな 短絡電流が流れることがわかる。また、S1のゲート-ソー ス波形 vgs1 がターンオフ後に振動しているが、これは高 dv/dt により S1 の帰還容量を通じて入力容量に電流が流れ るためである。一方、図12より提案回路では補助回路を動 作させることによって C1 を高速に充電できるため, S2 を オンさせるときの出力容量の電荷消費がなくなり短絡電流 を低減できる。また、提案回路では vgs1 の振動が従来回路 に比べて抑制されていることも確認できる。これは提案回 路では主素子のターンオフ時間は補助回路のインダクタと 出力容量の共振周波数で決定されるため, 従来回路と比べ て dv/dt が抑制されて、帰還容量を通じて大きな電流が流れ ないためである。従来回路と提案回路でS1のターンオフ時 間はそれぞれ 450 ns と 390 ns になり, ターンオフ時間を 13%改善でき、短絡電流も13.7Aから0Aまで低減するこ とができる。また、負荷力率 0.85 を一定とした条件での負 荷電力と効率の関係を図13に示す。同図からわかるように 41 W 以下の軽負荷領域において従来回路に比べて提案回路 の方が高効率であり、26 W 出力時に9.0 pt の効率改善を確 認できる。これは、従来回路では軽負荷時において主素子 出力容量の充放電時間が長くなり, デッドタイム期間中に 主素子出力容量の充放電を完了することができず, デッド タイム期間終了後に主素子をオンする際に短絡電流により ターンオン損失が発生するのに対し、提案回路では主素子

出力容量の充放電を高速に行うことができ, デッドタイム 期間終了後に主素子をオンする際のターンオン損失を低減 できるためである。重負荷時においては提案回路にくらべ て従来回路の方が高効率になるが、これは補助回路の損失 がないためである。41 W 以上の領域においては補助回路を 動作させないようにすることで従来回路と同等の効率を得 ることができる。また、14W出力時のデッドタイムと効率 の関係を図14に示す。同図よりデッドタイムが400 ns以下 で従来回路に比べて提案回路では高効率な運転が可能であ る。これは、従来回路ではデッドタイムが短いとその期間 中に主素子出力容量の充放電を行うことができないが、提 案回路ではデッドタイムが短くても出力容量の充放電を高 速に行えるためである。デッドタイム期間が 400 ns 以上で あれば提案回路に比べて従来回路の方が高効率となる。換 言すれば、デッドタイムが長くなると従来回路でもデッド タイム期間中に主素子出力容量の充放電が行えるため、 タ ーンオン損失が減少し効率が改善するからである (6)。デッ ドタイムが 250 ns のときに 21 pt の効率上昇を確認した。一 般的に電力変換器ではデッドタイムはスイッチング 1 周期 の 5 %以下にすることが望ましく, 100 kHz 駆動時では 500 ns 以下のデッドタイムが求められる <sup>(7)</sup>。100 kHz のような 高周波で軽負荷運転の場合, デッドタイム期間中に主素子 出力容量の充放電が行えないため、高速かつ高効率なスイ ッチングを実現するためには,本稿で提案したゲートドラ イブ電源昇圧補助回路を用いた手法が有効である。また, ハーフブリッジインバータのような電力変換器における損 失は、導通損とスイッチング損の合計であり、従来回路と 提案回路では負荷電流が等しいため、主素子の導通損はほ ぼ同じであると考えられる。よって、従来回路と比べ提案 回路の方が効率改善できるのはスイッチング損が減少した ためであり、提案する手法は MHz 級の高周波電力変換器に おいて、更に有効であると考えられる。

#### 4. まとめ

本稿では電力変換器の主スイッチング素子である MOSFET を高速にスイッチングするゲートドライブ電源昇 圧補助回路について述べた。補助回路のパラメータ設計に 関する検討を行い、設計した提案回路を降圧チョッパ、ハ ーフブリッジインバータに適用し、実験を通じて設計法の 妥当性と各種運転特性を検証した。

降圧チョッパでは効率は悪化するものの、軽負荷時においても  $100~\rm kHz$  駆動を実現し、 $50~\rm \%$ デューティーサイクル駆動時に実際のオンデューティーサイクルを  $66.4~\rm \%$ から  $52.0~\rm \%$ に  $14.4~\rm pt$  改善できることを確認した。更にターンオフ  $\rm dv/dt$  を  $0.16~\rm kV/\mu s$  から  $1.49~\rm kV/\mu s$  と約  $9~\rm Ge$  高速化できることも確認した。また、ハーフブリッジインバータでは  $14~\rm W$  出力の軽負荷時にターンオフ時間を  $450~\rm ns$  から  $390~\rm ns$  と  $13~\rm \%短縮し、効率も <math>35.0~\rm \%$ から  $66.0~\rm \%$ と最大  $21~\rm pt$  改善できることを確認した。

本稿で提案したゲートドライブ電源昇圧補助回路を用い

る手法は MOSFET の出力容量が大きい場合にさらに有効である。例えば、大電流化に対応するために MOSFET を並列駆動する場合や、各種寄生容量が大きな低オン抵抗の MOSFET を駆動する際に効果的である。

## 文 献

- (1) T. Noguchi, S. Yajima and H. Komatsu: "Development of Gate Drive Circuit for Next-Generation Ultra High-Speed Switching Devices", IEEJ Trans., Vol. 129-D, No. 1, pp. 46-52 (2009) (in Japanese)

- 野口季彦・矢島哲志・小松宏禎:「次世代超高速スイッチング素子ゲート駆動回路の開発」,電学論 D, Vol.129, No.1, pp. 46-52 (2009)

- (2) T. Noguchi and T. Mizuno: "High-Speed Switching Method of MOSFET Using Auxiliary Circuit Shorting Load: Application and Operation Characteristics of Chopper", IEEJ Trans., Vol. 132-D, No. 5, pp. 598-559 (2012) (in Japanese) 野口季彦・水野知博:「負荷短絡補助回路を用いた MOSFET の高速スイッチング法 ーチョッパへの適用と運転特性—」,電学論 D, Vol.132, No.5, pp.598-599 (2012)

- (3) T. Noguchi and T. Mizuno: "High-Speed Switching Method of MOSFET Using Auxiliary Circuit Shorting Load: Application and Operation Characteristics of High-Frequency Half-Bridge Inverter", IEEJ Trans., Vol. 132-D, No. 11, pp. 1080-1081 (2012) (in Japanese) 野口季彦・水野知博:「負荷短絡補助回路を用いた MOSFET の高速

- 野口季彦・水野知博: | 負荷短絡補助回路を用いた MOSFET の高速 スイッチング法 —高周波ハーフブリッジインバータへの適用と運 転特性—」, 電学論 D, Vol.132, No.11, pp.1080-1081 (2012)

- (4) M. Murata, T. Mizuno and T. Noguchi: "High-Speed Switching Method of MOSFET Using Voltage Boost Auxiliary Circuit Fed by Gate Drive Power Supply", IEEJ Proc. IAS Annual Conference, Vol.1, pp. 369-370 (2013) (in Japanese) 村田宗洋・水野知博・野口季彦:「ゲートドライブ電源昇圧補助回路を用いた MOSFET の高速スイッチング法」, 平成 25 年電気学会産業応用部門大会, Vol.1, pp. 369-370 (2013)

- (5) M. Murata and T. Noguchi: "High-Efficiency and High-Speed Switching Method of MOSFET Using Gate Drive Auxiliary Circuit", The Papers of Joint Technical Meeting on "Electron Devices" and "Power Converter", EDD-13-58, SPC-13-120 (2013) (in Japanese)

- 村田宗洋・野口季彦:「ゲートドライブ補助回路による MOSFET の 高効率高速スイッチング法」、電子デバイス・半導体電力変換合同研 究会資料, EDD-13-58, SPC-13-120 (2013)

- (6) N. Hoshi and A. Matsui: "Improvement of Power Conversion Efficiency of Soft-Switching Inverter in Range of Low Output Power by Adjustable Dead Time Control", IEEJ Trans., Vol.131-D, No.5, pp.679-684 (2011) (in Japanese) 星伸・・松井綾花:「可変デッドタイム制御によるソフトスイッチングインバータの低出力域での高効率化」, 電学論 D, Vol.131, No.5, pp.679-684 (2011)

- (7) K. Shirakawa, K. Wada and T. Shimizu: "An Issue on 200 kHz Class High Frequency Switching of a PWM Inverter", IEEJ Proc. IAS Annual Conference, Vol. 1, pp. 277-280 (2006) (in Japanese) 白川和博・和田圭二・清水敏久:「PWM インバータの 200 kHz 級高周波スイッチングの課題」, 平成 18 年電気学会産業応用部門大会, Vol. 1, pp. 277-280 (2006)

- (8) M. Ishigaki and H. Fujita: "A Resonant Gate-Drive Circuit Capable of High-Frequency and High-Efficiency Operation", IEEJ Trans, Vol. 127-D, No. 10, pp. 1090-1096 (2007) (in Japanese)

石垣将紀・藤田英明:「低損失・高周波動作可能な MOSFET 用共振 形ゲートドライブ回路」、電学論 D, Vol. 127, No. 10, pp. 1090-1096

- (9) 餅川宏・小山建夫:「小型・低損失インバータを実現する新回路技術」, 東芝レビュー2006 vol. 61, No. 11, pp. 32-35 (2006)